## SwitchReg™

# **General Description**

The AAT1230 is a high frequency, high efficiency boost converter capable of 18V maximum output voltage. The internal power switch can deliver 100mA load current. It is the ideal power solution to power OLED, LCD, and CCD applications operating from a single cell lithium-ion battery.

Hysteretic control provides up to 2MHz switching frequency and fast response to load transients with small, low-cost external components. The fully integrated control IC simplifies the design while reducing the total PCB footprint. The AAT1230 offers a true load disconnect feature which isolates the load from the power source when EN/SET is pulled low. This eliminates leakage current and maintains zero voltage at the output while disabled.

The output voltage can be dynamically set by activating one of two reference levels (FB1 or FB2) through the SEL logic pin. Optionally, AnalogicTech's Simple Serial Control™ (S²Cwire™) single wire interface provides dynamic programmability across a wide output voltage range through the EN/SET pin.

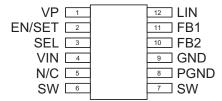

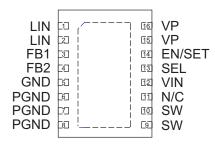

The AAT1230 is available in a Pb-free, thermally-enhanced 16-pin 3x4mm TDFN low-profile package or a Pb-free 12-pin TSOPJW package.

### **Features**

- V<sub>IN</sub> Range: 2.7V to 5.5V

- Maximum Output: 18V @ 100mA

- · True Load Disconnect

- · Dynamic Voltage Control Options

- Hysteretic Control

- No External Compensation Components

- Excellent Load Transient Response

- High Efficiency at Light Load

- Up to 2MHz Switching Frequency

- Ultra-Small Inductor and Capacitors

- Integrated Low R<sub>DS(ON)</sub> MOSFET Switches

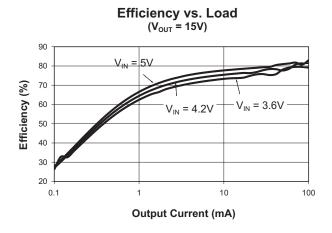

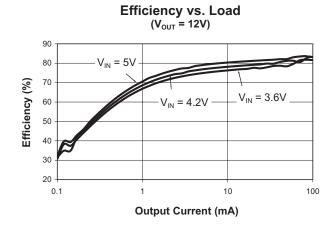

- Up to 85% Efficiency

- <1µA Shutdown Current</li>

- Integrated Soft Start

- Cycle-by-Cycle Current Limit

- Short-Circuit, Over-Temperature Protection

- Available in TSOPJW-12 or TDFN34-16 Package

- -40°C to +85°C Temperature Range

## **Applications**

- CCD Bias Circuit

- Digital Still Cameras

- · LCD Bias Circuit

- Mobile Handsets

- MP3 Players

- OLED Displays

- PDAs and Notebook PCs

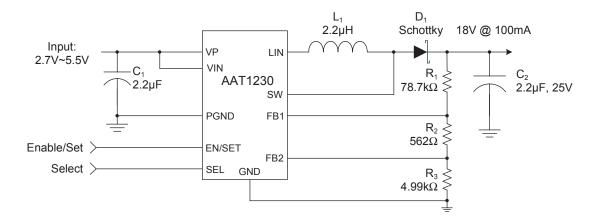

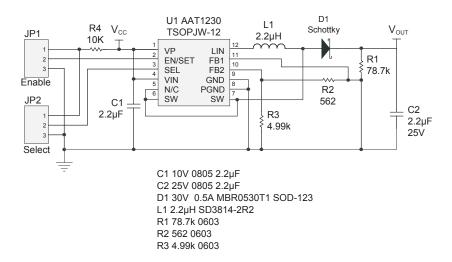

## **Typical Application**

# **Pin Descriptions**

| Pi<br>TSOPJW-12 | n #<br>TDFN34-16 | Symbol | Function                                                                                                                                                                          |

|-----------------|------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1               | 15, 16           | VP     | Input power pin; connected to the source of the P-channel MOSFET.  Connect to the input capacitor(s).                                                                             |

| 2               | 14               | EN/SET | IC active high enable pin. Alternately, input pin for S <sup>2</sup> Cwire control utilizing FB2 reference.                                                                       |

| 3               | 13               | SEL    | Logic high selects FB1 high output reference; logic low selects FB2 low output reference. Pull low for S2Cwire control.                                                           |

| 4               | 12               | VIN    | Input voltage for the converter. Connect this pin directly to the VP pin.                                                                                                         |

| 5               | 11               | N/C    | No connection.                                                                                                                                                                    |

| 6, 7            | 9, 10            | SW     | Boost converter switching node. Connect the power inductor between this pin and LIN pin.                                                                                          |

| 8               | 6, 7, 8          | PGND   | Power ground for the boost converter; connected to the source of the N-channel MOSFET. Connect to the input and output capacitor return.                                          |

| 9               | 5                | GND    | Ground pin.                                                                                                                                                                       |

| 10              | 4                | FB2    | Feedback pin for low output voltage set point. Pin set to 0.6V when SEL is low and disabled when SEL is high. Voltage is set from 0.6V to 1.2V with S <sup>2</sup> Cwire control. |

| 11              | 3                | FB1    | Feedback pin for high output voltage set point. Pin set to 1.2V when SEL is high and disabled when SEL is low. Disabled with S <sup>2</sup> Cwire control.                        |

| 12              | 1, 2             | LIN    | Switched power input. Connected to the power inductor.                                                                                                                            |

| N/A             | EP               |        | Exposed paddle (bottom). Tied to SW pins. May be connected to SW pins or left floating.                                                                                           |

# **Pin Configuration**

TSOPJW-12 (Top View)

TDFN34-16 (Top View)

# Absolute Maximum Ratings<sup>1</sup>

$T_A = 25$ °C, unless otherwise noted.

| Symbol                                     | Description                                      | Value                 | Units |

|--------------------------------------------|--------------------------------------------------|-----------------------|-------|

| V <sub>IN</sub>                            | Input Voltage                                    | -0.3 to 6.0           | V     |

| SW                                         | Switching Node                                   | 20                    | V     |

| L <sub>IN</sub> , EN/SET,<br>SEL, FB1, FB2 | Maximum Rating                                   | V <sub>IN</sub> + 0.3 | V     |

| T <sub>J</sub>                             | Operating Temperature Range                      | -40 to 150            | °C    |

| T <sub>S</sub>                             | Storage Temperature Range                        | -65 to 150            | °C    |

| T <sub>LEAD</sub>                          | Maximum Soldering Temperature (at leads, 10 sec) | 300                   | °C    |

# **Recommended Operating Conditions**

| Symbol         | Description                                       | Value      | Units |       |  |

|----------------|---------------------------------------------------|------------|-------|-------|--|

| 0              | Thermal Resistance                                | TDFN34-16  | 44    | °C/W  |  |

| $\theta_{JA}$  | TSOPJW-12                                         |            | 160   | C/VV  |  |

| В              | Maximum Dower Dissipation (T 2500)                | TDFN34-16  |       | mW    |  |

| $P_{D}$        | Maximum Power Dissipation (T <sub>A</sub> = 25°C) | TSOPJW-12  | 625   | IIIVV |  |

| T <sub>J</sub> | Operating Temperature Range                       | -40 to 150 | °C    |       |  |

<sup>1.</sup> Stresses above those listed in Absolute Maximum Ratings may cause permanent damage to the device. Functional operation at conditions other than the operating conditions specified is not implied. Only one Absolute Maximum Rating should be applied at any one time.

## Electrical Characteristics<sup>1</sup>

$\overline{T_A}$  = -40°C to +85°C, unless otherwise noted. Typical values are  $T_A$  = 25°C,  $V_{IN}$  = 3.6V.

| Symbol                     | Description                                        | Conditions                                                 | Min   | Тур  | Max   | Units |

|----------------------------|----------------------------------------------------|------------------------------------------------------------|-------|------|-------|-------|

| Power Suppl                | y                                                  |                                                            | '     |      |       |       |

| V <sub>IN</sub>            | Input Voltage Range                                |                                                            | 2.7   |      | 5.5   | V     |

| V <sub>OUT(MAX)</sub>      | Maximum Output Voltage                             |                                                            |       |      | 18    | V     |

|                            |                                                    | V <sub>IN</sub> Rising                                     |       |      | 2.7   | V     |

| $V_{UVLO}$                 | UVLO Threshold                                     | Hysteresis                                                 |       | 150  |       | mV    |

|                            |                                                    | V <sub>IN</sub> Falling                                    | 1.8   |      |       | V     |

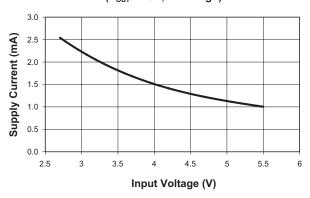

|                            |                                                    | SEL = GND, V <sub>OUT</sub> = 14V,                         |       | 2.0  |       | mA    |

| Ι <sub>Q</sub>             | Quiescent Current                                  | I <sub>OUT</sub> = 0, Switching <sup>2</sup>               |       | 2.0  |       | шд    |

| 'Q                         | Quiescent Carrent                                  | SEL = GND, FB2 = 1.5V,                                     |       | 40   | 70    | μA    |

|                            |                                                    | Not Switching                                              |       | 10   |       | μπ    |

| I <sub>SHDN</sub>          | V <sub>IN</sub> Pin Shutdown Current               | EN/SET = GND                                               |       |      | 1.0   | μA    |

| I <sub>OUT</sub>           | Output Current                                     | 2.7V < V <sub>IN</sub> < 5.5V, V <sub>OUT</sub> = 18V      |       |      | 100   | mA    |

| FB1                        | FB1 Reference Voltage                              | $I_{OUT} = 0$ to 100mA, $V_{IN} = 2.7V$                    | 1.164 | 1.2  | 1.236 | V     |

|                            | · - · · · · · · · · · · · · · · · · · ·            | to 5.0V, SEL = High                                        | 1     |      |       |       |

| FB2                        | FB2 Reference Voltage                              | $I_{OUT}$ = 0 to 100mA, $V_{IN}$ = 2.7V to 5.0V, SEL = Low | 0.582 | 0.6  | 0.618 | V     |

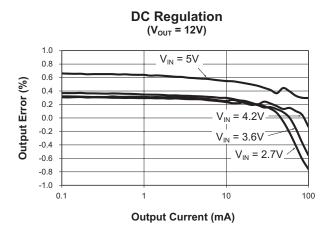

| $\Delta V_{LOADREG}$       | Load Regulation                                    | I <sub>OUT</sub> = 0 to 100mA                              |       | 0.01 |       | %/mA  |

| $\Delta V_{LINEREG}$       |                                                    |                                                            |       |      |       |       |

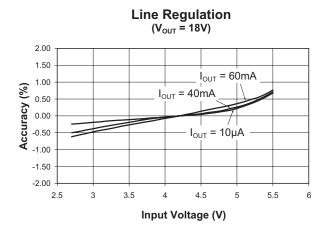

| $\Delta V_{IN}$            | Line Regulation                                    | $V_{IN} = 2.7V \text{ to } 5.5V$                           |       | 0.6  |       | %/V   |

| R <sub>DS(ON)L</sub>       | Low Side Switch On Resistance                      |                                                            |       | 0.06 |       | Ω     |

| R                          | Input Disconnect Switch                            |                                                            |       | 0.18 |       | Ω     |

| R <sub>DS(ON)IN</sub>      | On Resistance                                      |                                                            |       | 0.10 |       | 22    |

| T <sub>SS</sub>            | Soft-Start Time                                    | From Enable to Output Regulation;                          |       | 350  |       | μs    |

|                            |                                                    | V <sub>OUT</sub> = 15V                                     |       |      |       |       |

| $T_{SD}$                   | Over-Temperature Shutdown                          |                                                            |       | 140  |       | °C    |

|                            | Threshold                                          |                                                            |       | 45   |       | 00    |

| T <sub>HYS</sub>           | Shutdown Hysteresis                                | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \                      |       | 15   |       | °C    |

| I <sub>LIM</sub>           | N-Channel Current Limit                            | V <sub>IN</sub> = 3.6V                                     |       | 3.0  |       | Α     |

| SEL, EN/SET                |                                                    | \/ - 0.7\/                                                 |       | 1    | 0.4   | \/    |

| V <sub>SEL(L)</sub>        | SEL Threshold Ligh                                 | $V_{IN} = 2.7V$                                            | 1 4   |      | 0.4   | V     |

| V <sub>SEL(H)</sub>        | SEL Threshold High Enable Threshold Low            | $V_{IN} = 5.5V$                                            | 1.4   |      | 0.4   | V     |

| V <sub>EN/SET(L)</sub>     |                                                    | $V_{IN} = 2.7V$                                            | 1 4   |      | 0.4   | V     |

| V <sub>EN/SET(H)</sub>     | Enable Threshold High                              | V <sub>IN</sub> = 5.5V                                     | 0.3   |      | 75    |       |

| T <sub>EN/SET LO</sub>     | EN/SET Low Time                                    |                                                            | 0.3   | 50   | /5    | μs    |

| T <sub>EN/SET HI MIN</sub> | Minimum EN/SET High Time  Maximum EN/SET High Time |                                                            | -     | 50   | 75    | ns    |

| T <sub>EN/SET HI MAX</sub> | EN/SET Off Timeout                                 |                                                            |       |      |       | μs    |

| T <sub>OFF</sub>           | EN/SET Latch Timeout                               |                                                            | -     |      | 500   | μs    |

| T <sub>LAT</sub>           | EN/SET Latch Timeout EN/SET Input Leakage          |                                                            | -1    |      | 500   | μs    |

| I <sub>EN/SET</sub>        | EIWOET IIIput Leakage                              |                                                            | -1    |      | l I   | μΑ    |

<sup>1.</sup> The AAT1230 is guaranteed to meet performance specifications from 0°C to 70°C. Specification over the -40°C to +85°C operating temperature range is assured by design, characterization, and correlation with statistical process controls.

<sup>2.</sup> Total input current with prescribed FB resistor network can be reduced with larger resistor values.

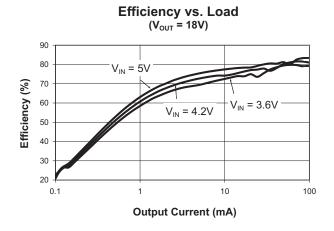

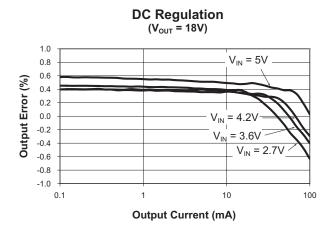

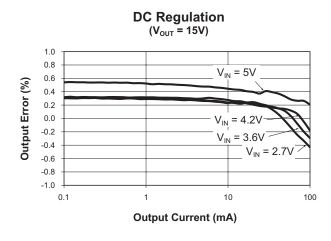

# **Typical Characteristics**

# **Typical Characteristics**

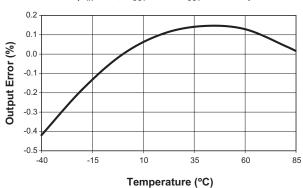

Output Voltage Error vs. Temperature  $(V_{IN} = 5V; V_{OUT} = 18V; I_{OUT} = 100mA)$

No Load Input Current vs. Input Voltage (V<sub>OUT</sub> = 18V; EN = High)

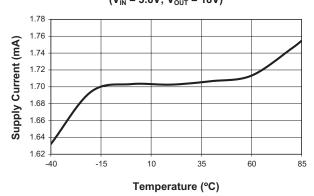

No Load Input Current vs. Temperature (V<sub>IN</sub> = 3.6V; V<sub>OUT</sub> = 18V)

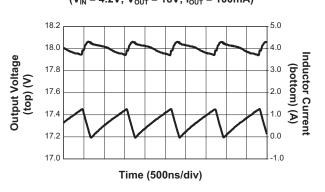

Output Ripple  $(V_{IN} = 4.2V; V_{OUT} = 18V; I_{OUT} = 100mA)$

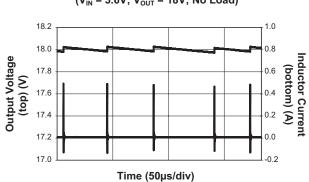

Output Ripple  $(V_{IN} = 3.6V; V_{OUT} = 18V; No Load)$

## **Typical Characteristics**

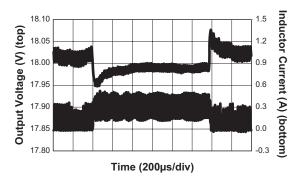

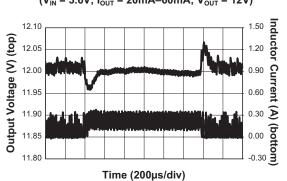

#### **Load Transient Response**

$(V_{IN} = 4.2V; I_{OUT} = 20mA-60mA; V_{OUT} = 18V)$

# Load Transient Response (V<sub>IN</sub> = 3.6V; I<sub>OUT</sub> = 20mA-60mA; V<sub>OUT</sub> = 12V)

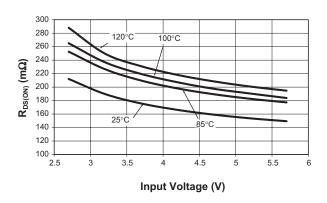

## P-Channel $R_{\text{DS(ON)}}$ vs. Input Voltage

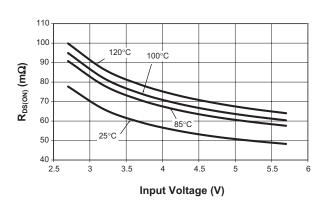

#### N-Channel R<sub>DS(ON)</sub> vs. Input Voltage

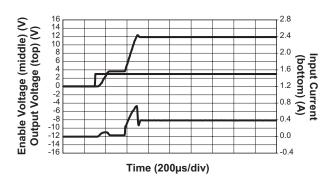

$\begin{array}{c} \textbf{Soft Start} \\ \textbf{(V}_{\text{IN}} = 3.6 \text{V}; \ \textbf{C}_{\text{IN}} = 2.2 \mu \text{F}; \ \textbf{I}_{\text{OUT}} = 100 \text{mA}; \ \textbf{V}_{\text{OUT}} = 12 \text{V)} \end{array}$

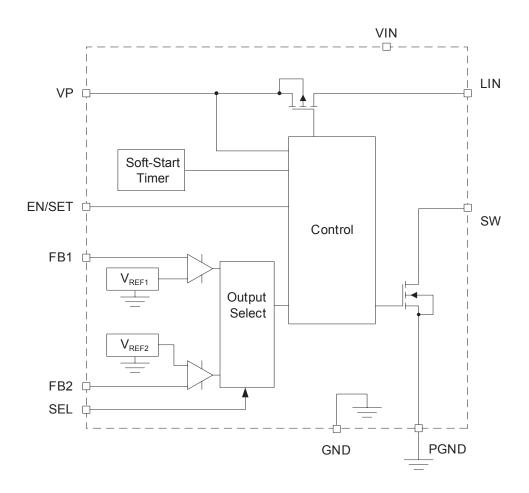

## **Functional Block Diagram**

# **Functional Description**

The AAT1230 consists of a DC/DC boost controller, an integrated slew rate controlled input disconnect MOSFET switch, and a MOSFET power switch. A high voltage rectifier, power inductor, output capacitor, and resistor divider network are required to implement a DC/DC boost converter.

### **Control Loop**

The AAT1230 provides the benefits of current mode control with a simple hysteretic feedback loop. The device maintains exceptional DC regulation, transient response, and cycle-by-cycle current limit without additional compensation components.

The AAT1230 modulates the power MOSFET switching current in response to changes in output voltage. This allows the voltage loop to directly program the required inductor current in response to changes in the output load.

The switching cycle initiates when the N-channel MOSFET is turned ON and current ramps up in the inductor. The ON interval is terminated when the inductor current reaches the programmed peak current level. During the OFF interval, the input current decays until the lower threshold, or zero inductor current, is reached. The lower current is equal to the peak current minus a preset hysteresis threshold - which determines the inductor ripple current. The peak current is adjusted by the controller until the output current requirement is met.

The magnitude of the feedback error signal determines the average input current. Therefore, the AAT1230 controller implements a programmed current source connected to the output capacitor and load resistor. There is no right-half plane zero, and loop stability is achieved with no additional compensation components.

Increased load current results in a drop in the output feedback voltage (FB1 or FB2) sensed through the feedback resistors (R1, R2, R3). The controller responds by increasing the peak inductor current, resulting in higher average current in the inductor. Alternatively, decreased output load results in an increase in the output feedback voltage (FB1 or FB2 pin). The controller responds by decreasing the peak inductor current, resulting in lower average current in the inductor.

At light load, the inductor OFF interval current goes below zero and the boost converter enters discontinuous mode operation. Further reduction in the load results in a corresponding reduction in the switching frequency. The AAT1230 provides pulsed frequency operation which reduces switching losses and maintains high efficiency at light loads.

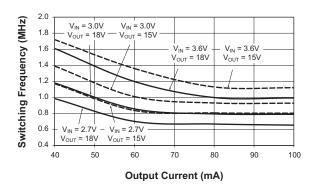

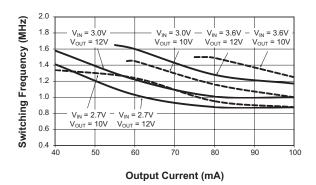

Operating frequency varies with changes in the input voltage, output voltage, and inductor size. Once the boost converter has reached continuous mode, further increases in the output load will not significantly change the operating frequency. A small  $2.2\mu H$  ( $\pm 20\%$ ) inductor is selected to maintain high frequency switching (up to 2MHz) and high efficiency operation for outputs from 10V to 18V.

## Output Voltage Programming

The output voltage may be programmed through a resistor divider network located from output capacitor to FB1/FB2 pins to ground. Pulling the SEL pin high activates the FB1 pin which maintains a 1.2V reference voltage, while the FB2 reference is disabled. Pulling the SEL pin low activates the FB2 pin which maintains a 0.6V reference, while the FB1 reference is disabled. This function allows dynamic selection between two distinct output voltages across a 2X range (maximum). An additional resistor between FB1 and FB2 allows the designer to program the outputs across a reduced <2X range.

Alternatively, the output voltage may be dynamically programmed to any of 16 voltage levels using the S<sup>2</sup>Cwire serial digital input. The single wire S<sup>2</sup>Cwire interface provides high-speed output voltage programmability across a 2X output voltage range. S<sup>2</sup>Cwire functionality is enabled by pulling the SEL pin low and providing S<sup>2</sup>Cwire digital clock input to the EN/SET pin. Table 2 details the FB2 reference voltage versus S<sup>2</sup>Cwire rising clock edges.

#### Soft Start / Enable

The input disconnect switch is activated when a valid input voltage is present and the EN/SET pin is pulled high. The slew rate control on the P-channel MOSFET ensures minimal inrush current as the output voltage is charged to the input voltage, prior to switching of the N-channel power MOSFET. Monotonic turn-on is guaranteed by the built-in soft-start circuitry. Soft-start eliminates output voltage overshoot across the full input voltage range and all loading conditions.

# **Current Limit and Over-Temperature Protection**

The switching of the N-channel MOSFET terminates when current limit of 3.0A (typical) is exceeded. This minimizes power dissipation and component stresses under overload and short-circuit conditions. Switching resumes when the current decays below the current limit.

Thermal protection disables the AAT1230 when internal dissipation becomes excessive. Thermal protection disables both MOSFETs. The junction over-temperature threshold is 140°C with -15°C of temperature hysteresis. The output voltage automatically recovers when the over-temperature or over-current fault condition is removed.

#### **Under-Voltage Lockout**

Internal bias of all circuits is controlled via the  $V_{\text{IN}}$  input. Under-voltage lockout (UVLO) guarantees sufficient  $V_{\text{IN}}$  bias and proper operation of all internal circuitry prior to soft start.

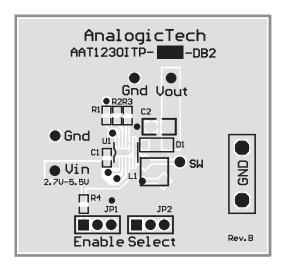

Figure 1: AAT1230 Demo Board Schematic.

## **Application Information**

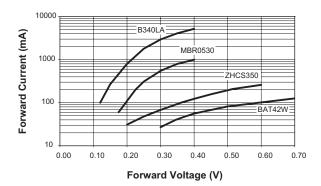

## **Selecting the Output Diode**

To ensure minimum forward voltage drop and no recovery, high voltage Schottky diodes are considered the best choice for the AAT1230 boost converter. The AAT1230 output diode is sized to maintain acceptable efficiency and reasonable operating junction temperature under full load operating conditions. Forward voltage ( $V_F$ ) and package thermal resistance ( $\theta_{JA}$ ) are the dominant factors to consider in selecting a diode. The diode's published current rating may not reflect actual operating conditions and should be used only as a comparative measure between similarly rated devices. 20V rated Schottky diodes are recommended for outputs less than 15V, while 30V rated Schottky diodes are recommended for outputs greater than 15V.

The switching period is divided between ON and OFF time intervals.

$$\frac{1}{F_S} = T_{ON} + T_{OFF}$$

During the ON time, the N-channel power MOS-FET is conducting and storing energy in the boost inductor. During the OFF time, the N-channel power MOSFET is not conducting. Stored energy is transferred from the input battery and boost induc-

tor to the output load through the output diode. Duty cycle is defined as the ON time divided by the total switching interval.

$$D = \frac{T_{ON}}{T_{ON} + T_{OFF}}$$

$$= T_{ON} \cdot F_{S}$$

The maximum duty cycle can be estimated from the relationship for a continuous mode boost converter. Maximum duty cycle ( $D_{MAX}$ ) is the duty cycle at minimum input voltage ( $V_{IN(MIN)}$ ).

$$D_{MAX} = \frac{V_{OUT} - V_{IN(MIN)}}{V_{OUT}}$$

The average diode current during the OFF time can be estimated.

$$I_{AVG(OFF)} = \frac{I_{OUT}}{1 - D_{MAX}}$$

The following curves show the  $V_F$  characteristics for different Schottky diodes (100°C case). The  $V_F$  of the Schottky diode can be estimated from the average current during the off time.

The average diode current is equal to the output current.

$$I_{AVG(TOT)} = I_{OUT}$$

The average output current multiplied by the forward diode voltage determines the loss of the output diode.

$$P_{LOSS(DIODE)} = I_{AVG(TOT)} \cdot V_{F}$$

$$= I_{OUT} \cdot V_{F}$$

Diode junction temperature can be estimated.

$$T_{J(DIODE)} = T_{AMB} + \Theta_{JA} \cdot P_{LOSS(DIODE)}$$

Output diode junction temperature should be maintained below 110°C, but may vary depending on application and/or system guidelines. The diode  $\theta_{\text{JA}}$  can be minimized with additional PCB area on the cathode. PCB heatsinking the anode may degrade EMI performance.

The reverse leakage current of the rectifier must be considered to maintain low quiescent (input) current and high efficiency under light load. The rectifier reverse current increases dramatically at high temperatures.

## Selecting the Boost Inductor

The AAT1230 controller utilizes hysteretic control and the switching frequency varies with output load and input voltage. The value of the inductor determines the maximum switching frequency of the AAT1230 boost converter. Increased output inductance decreases the switching frequency, resulting in higher peak currents and increased output voltage ripple. To maintain 2MHz maximum switching frequency and stable operation, an output inductor sized from 1.5µH to 2.7µH is recommended.

A better estimate of  $D_{\text{MAX}}$  is possible when  $V_{\text{F}}$  is known.

$$D_{MAX} = \frac{(V_{OUT} + V_F - V_{IN(MIN)})}{(V_{OUT} + V_F)}$$

Where  $V_F$  is the Schottky diode forward voltage. If not known, it can be estimated at 0.5V. Manufacturer's specifications list both the inductor DC current rating, which is a thermal limitation, and peak inductor current rating, which is determined by the saturation characteristics. Measurements at full load and high ambient temperature should be completed to ensure that the inductor does not saturate or exhibit excessive temperature rise.

The output inductor (L) is selected to avoid saturation at minimum input voltage, maximum output load conditions. Peak current may be estimated using the following equation, assuming continuous conduction mode. Worst-case peak current occurs at minimum input voltage (maximum duty cycle) and maximum load. Switching frequency can be estimated from the curves and assumes a 2.2µH inductor.

$$I_{PEAK} = \frac{I_{OUT}}{(1 - D_{MAX})} + \frac{D_{MAX} \cdot V_{IN(MIN)}}{(2 \cdot F_{SW} \cdot L)}$$

At light load and low output voltage, the controller reduces the operating frequency to maintain maximum operating efficiency. As a result, further reduction in output load does not reduce the peak current. Minimum peak current can be estimated from 0.5A to 0.75A.

The RMS current flowing through the boost inductor is equal to the DC plus AC ripple components. Under worst-case RMS conditions, the current waveform is critically continuous. The resulting RMS calculation yields worst-case inductor loss. The RMS current value should be compared against the manufacturer's temperature rise, or thermal derating, guidelines.

$$I_{RMS} = \frac{I_{PEAK}}{\sqrt{3}}$$

For a given inductor type, smaller inductor size leads to an increase in DCR winding resistance and, in most cases, increased thermal impedance. Winding resistance degrades boost converter efficiency and increases the inductor's operating temperature.

$$\mathsf{P}_{\mathsf{LOSS}(\mathsf{INDUCTOR})} = \mathsf{I}_{\mathsf{RMS}}^{2} \cdot \mathsf{DCR}$$

To ensure high reliability, the inductor temperature should not exceed 100°C. In some cases, PCB heatsinking applied to the AAT1230  $L_{\rm IN}$  node (nonswitching) can improve the inductor's thermal capability. PCB heatsinking may degrade EMI per-

formance when applied to the SW node (switching) of the AAT1230.

Shielded inductors provide decreased EMI and may be required in noise sensitive applications. Unshielded chip inductors provide significant space savings at a reduced cost compared to shielded (wound and gapped) inductors. In general, chiptype inductors have increased winding resistance (DCR) when compared to shielded, wound varieties.

### **Selecting the Boost Capacitors**

The high output ripple inherent in the boost converter necessitates low impedance output filtering. Multi-layer ceramic (MLC) capacitors provide small size and adequate capacitance, low parasitic equivalent series resistance (ESR) and equivalent series inductance (ESL), and are well suited for use with the AAT1230 boost regulator. MLC capacitors of type X7R or X5R are recommended to ensure good capacitance stability over the full operating temperature range.

The output capacitor is sized to maintain the output load without significant voltage droop ( $\Delta V_{OUT}$ ) during the power switch ON interval, when the output diode is not conducting. A ceramic output capacitor from 2.2µF to 4.7µF is recommended. Typically, 25V rated capacitors are required for the 18V boost output. Ceramic capacitors sized as small as 0805 are available which meet these requirements.

MLC capacitors exhibit significant capacitance reduction with applied voltage. Output ripple measurements should confirm that output voltage droop is acceptable. Voltage derating can minimize this factor, but results may vary with package size and among specific manufacturers.

Output capacitor size can be estimated at a switching frequency ( $F_{SW}$ ) of 500kHz (worst-case).

$$C_{OUT} = \frac{I_{OUT} \cdot D_{MAX}}{F_{SW} \cdot \Delta V_{OUT}}$$

The boost converter input current flows during both ON and OFF switching intervals. The input ripple current is less than the output ripple and, as a result, less input capacitance is required. A ceramic output capacitor from 1µF to 3.3µF is recommended.

Minimum 6.3V rated ceramic capacitors are required at the input. Ceramic capacitors sized as small as 0603 are available which meet these requirements.

The AAT1230 provides excellent load transient response, but large capacitance tantalum or solid-electrolytic capacitors may be desired. These can replace (or be used in parallel with) ceramic capacitors. Both tantalum and OSCON-type capacitors are suitable due to their low ESR and excellent temperature stability (although they exhibit much higher ESR than MLC capacitors). Aluminum-electrolytic types are less suitable due to their high ESR characteristics and temperature drift. Unlike MLC capacitors, these types are polarized and proper orientation on input and output pins is required. 30% to 70% voltage derating is recommended for tantalum capacitors.

### **Setting the Output Voltage**

The output voltage may be programmed through a resistor divider network located from the output to FB1 and FB2 pins to ground. Pulling the SEL pin high activates the FB1 pin which maintains a 1.2V reference voltage, while the FB2 reference is disabled. Pulling the SEL pin low activates the FB2 pin which maintains a 0.6V reference, while the FB1 reference is disabled.

The AAT1230 output voltage can be programmed by one of three methods. First, the output voltage can be static by pulling the SEL logic pin either high or low. Second, the output voltage can be dynamically adjusted between two pre-set levels within a 2X operating range by toggling the SEL logic pin. Third, the output can be dynamically adjusted to any of 16 preset levels within a 2X operating range using the integrated S<sup>2</sup>Cwire single wire interface via the EN/SET pin.

#### **Option 1: Static Output Voltage**

A static output voltage can be configured by pulling the SEL either high or low. SEL pin high activates the FB1 reference pin to 1.2V (nominal). Alternatively, the SEL pin is pulled low to activate the FB2 reference at 0.6V (nominal). Table 1 provides details of resistor values for common output voltages from 10V to 18V for SEL = High and SEL = Low options.

In the static configuration, the FB1 pin should be directly connected to FB2. The resistor between

FB1 and FB2 pins is not required. See Table 1 for static output voltages with SEL = High or SEL = Low. SEL = High corresponds to  $V_{OUT(1)}$  and SEL = Low corresponds to  $V_{OUT(2)}$ .

#### Option 2: Dynamic Voltage Control Using SEL Pin

The output may be dynamically adjusted between two output voltages by toggling the SEL logic pin. Output voltages  $V_{OUT(1)}$  and  $V_{OUT(2)}$  correspond to the two output references, FB1 and FB2. Pulling the SEL logic pin high activates  $V_{OUT(1)}$ , while pulling the SEL logic pin low activates  $V_{OUT(2)}$ .

The minimum output voltage must be greater than the specified maximum input voltage plus margin to maintain proper operation of the AAT1230 boost converter. In addition, the ratio of output voltages  $V_{\text{OUT}(2)}/V_{\text{OUT}(1)}$  is always less than 2.0, corresponding to a 2X (maximum) programmable range.

See Table 1 for dynamic output voltage settings when toggling between SEL = High and SEL = Low. SEL = High corresponds to  $V_{OUT(1)}$  and SEL = Low corresponds to  $V_{OUT(2)}$ .

| VOUT(1)                             | VOLIT(2)    | R3 =    | 4.99kΩ  |

|-------------------------------------|-------------|---------|---------|

| V <sub>OUT(1)</sub><br>(SEL = High) | (SEL = Low) | R1 (kΩ) | R2 (kΩ) |

| 10.0V                               | _           | 36.5    | _       |

| 12.0V                               | _           | 44.2    | _       |

| 15.0V                               | _           | 57.6    | _       |

| 16.0V                               | _           | 61.9    | _       |

| 18.0V                               | _           | 69.8    | _       |

| _                                   | 10.0V       | 78.7    | _       |

| _                                   | 12.0V       | 95.3    | _       |

| _                                   | 15.0V       | 121     | _       |

| _                                   | 16.0V       | 127     | _       |

| _                                   | 18.0V       | 143     | _       |

| 12.0V                               | 10.0V       | 75      | 3.32    |

| 15.0V                               | 10.0V       | 76.8    | 1.65    |

| 16.0V                               | 10.0V       | 76.8    | 1.24    |

| 18.0V                               | 10.0V       | 78.7    | 0.562   |

| 15.0V                               | 12.0V       | 90.9    | 3.65    |

| 16.0V                               | 12.0V       | 93.1    | 2.49    |

| 18.0V                               | 12.0V       | 93.1    | 1.65    |

| 18.0V                               | 15.0V       | 115     | 3.32    |

Table 1: SEL Pin Voltage Control Resistor Values (1% resistor tolerance).

# Option 3: Dynamic Voltage Control Using S<sup>2</sup>Cwire Interface

The output can be dynamically adjusted by the host controller to any of 16 pre-set output voltage levels using the integrated S<sup>2</sup>Cwire interface. The EN/SET pin serves as the S<sup>2</sup>Cwire interface input. The SEL pin must be pulled low when using the S<sup>2</sup>Cwire interface.

#### S<sup>2</sup>Cwire Serial Interface

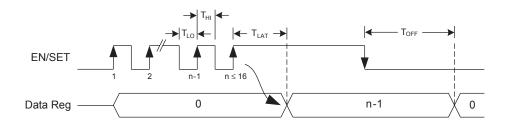

AnalogicTech's S²Cwire serial interface is a proprietary high-speed single-wire interface available only from AnalogicTech. The S²Cwire interface records rising edges of the EN/SET input and decodes into 16 different states. Each state corresponds to a voltage setting on the FB2 pin, as shown in Table 2.

#### S<sup>2</sup>Cwire Serial Interface Timing

The S²Cwire serial interface has flexible timing. Data can be clocked-in at speeds up to 1MHz. After data has been submitted, EN/SET is held high to latch the data for a period  $T_{LAT}$ . The output is subsequently changed to the predetermined voltage. When EN/SET is set low for a time greater than  $T_{OFF}$ , the AAT1230 is disabled. When disabled, the register is reset to the default value, which sets the FB2 pin to 0.6V if EN is subsequently pulled high.

## S<sup>2</sup>Cwire Output Voltage Programming

The AAT1230 is programmed through the S²Cwire interface according to Table 2. The rising clock edges received through the EN/SET pin determine the feedback reference and output voltage setpoint. Upon power up with the SEL pin low and prior to S²Cwire programming, the default feedback reference voltage is set to 0.6V.

| EN/SET<br>Rising<br>Edges | FB2<br>Reference<br>Voltage (V) | EN/SET<br>Rising<br>Edges | FB2<br>Reference<br>Voltage (V) |

|---------------------------|---------------------------------|---------------------------|---------------------------------|

| 1                         | 0.60 (Default)                  | 9                         | 0.92                            |

| 2                         | 0.64                            | 10                        | 0.96                            |

| 3                         | 0.68                            | 11                        | 1.00                            |

| 4                         | 0.72                            | 12                        | 1.04                            |

| 5                         | 0.76                            | 13                        | 1.08                            |

| 6                         | 0.80                            | 14                        | 1.12                            |

| 7                         | 0.84                            | 15                        | 1.16                            |

| 8                         | 0.88                            | 16                        | 1.20                            |

Table 2: S<sup>2</sup>Cwire Voltage Control Settings (SEL = Low).

Figure 3: S<sup>2</sup>Cwire Timing Diagram to Program the Output Voltage.

## **PCB Layout Guidelines**

Boost converter performance can be adversely affected by poor layout. Possible impact includes high input and output voltage ripple, poor EMI performance, and reduced operating efficiency. Every attempt should be made to optimize the layout in order to minimize parasitic PCB effects (stray resistance, capacitance, inductance) and EMI coupling from the high frequency SW node.

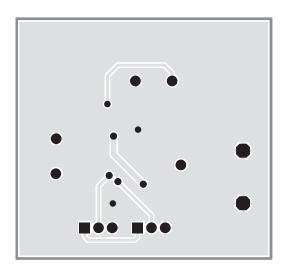

A suggested PCB layout for the AAT1230 boost converter is shown in Figures 1 and 2. The following PCB layout guidelines should be considered:

Minimize the distance from Capacitor C1 and C2 negative terminal to the PGND pins. This is especially true with output capacitor C2, which conducts high ripple current from the output diode back to the PGND pins.

- Place the feedback resistors close to the output terminals. Route the output pin directly to resistor R1 to maintain good output regulation. R3 should be routed close to the output GND pin, but should not share a significant return path with output capacitor C2.

- 3. Minimize the distance between L1 to D1 and switching pin SW; minimize the size of the PCB area connected to the SW pin.

- 4. Maintain a ground plane and connect to the IC RTN pin(s) as well as the GND terminals of C1 and C2.

- Consider additional PCB area on D1 cathode to maximize heatsinking capability. This may be necessary when using a diode with a high V<sub>F</sub> and/or thermal resistance.

- When using the TDFN33-12 package, connect paddle to SW pin or leave floating. Do not connect to RTN/GND conductors.

Figure 1: AAT1230 Evaluation Board Top Side.

Figure 2: AAT1230 Evaluation Board Bottom Side.

## **Boost Converter Design Example**

## **Specification**

$V_{OUT} = 16V$

$I_{OUT} = 100mA$

$V_{IN}$  = 2.7V to 4.2V (3.6V nominal)

$T_{AMB} = 50^{\circ}C$

## **Schottky Diode**

$$D_{MAX} = \frac{V_{O} - V_{IN(MIN)}}{V_{IN(MIN)}} = \frac{16 - 2.7}{2.7} = 0.831$$

$$I_{OFF(DIODE)} = \frac{I_{OUT}}{1 - D_{MAX}} = \frac{0.1A}{1 - 0.831} = 0.592A = 592mA$$

For Schottky diode MBR0530,  $V_F \approx 0.32$  @ 600mA,  $\theta_{JA} \approx 206$  °C/W in SOD-123 package.

$$P_{LOSS(DIODE)} = I_{OUT} \cdot V_F = (0.1A)(0.32V) = 0.032W = 32mW$$

$$T_{J(DIODE)} = T_{AMB} + \theta_{JA} \cdot P_{LOSS(DIODE)}$$

= 50 + 206 \cdot (0.032)

= 50 + 6.6

= 56.6 \cdot C

#### **16V Output Inductor**

$$D_{MAX} = \frac{V_{OUT} + V_F - V_{IN(MIN)}}{V_{OUT} + V_F}$$

$$= \frac{16 + 0.32 - 2.7}{16 + 0.32} = 0.834$$

From Switching Frequency vs.  $I_{OUT}$  curves estimated switching frequency of AAT1230 with  $V_{OUT}$  = 16V and  $I_{OUT}$  = 100mA,  $F_{SW}$  = 800kHz.

$$\begin{split} I_{PEAK} &= \frac{I_{OUT}}{1 - D_{MAX}} + \frac{D_{MAX} \cdot V_{IN(MIN)}}{(2 \cdot F_{SW} \cdot L)} \\ &= \frac{0.100}{1 - 0.840} + \frac{0.834 \ (2.7V)}{2 \cdot 0.8M \cdot 2.2\mu H} \\ &= 0.625 + 0.640 \\ &= 1.265A = 1265mA \\ I_{RMS} &= \frac{I_{PEAK}}{\sqrt{3}} = \frac{1265}{\sqrt{3}} = 730mA \end{split}$$

For Coiltronics inductor SD3814-2R2,  $I_{SAT}$  = 1.90A,  $I_{DC(MAX)}$  = 1.90A and DCR = 77m $\Omega$ .

$$P_{LOSS(INDUCTOR)} = I_{RMS}^{2} \cdot DCR$$

=  $(0.730)^{2} (0.077)$

=  $0.041W$

=  $41mW$

## **16V Output Capacitor**

$$\begin{split} \Delta V_{\text{OUT}} &= 0.2V \\ C_{\text{OUT}} &= \frac{I_{\text{OUT}} \cdot D_{\text{MAX}}}{F_{\text{SW}} \cdot \Delta V_{\text{OUT}}} = \frac{(0.1\text{A}) \, (0.84)}{(0.8\text{kHz}) \, (0.1V)} \\ &= 1.05 \mu \text{F}; \, \text{use} \, 2.2 \mu \text{F} / 25 \text{V MLC} \end{split}$$

#### **AAT1230 Losses**

$$I_{RMS} = I_{PEAK} \cdot \sqrt{\frac{D_{MAX}}{3}}$$

$$= 1.270 \sqrt{\frac{0.834}{3}}$$

$$= 0.527A$$

$$= 527mA$$

From datasheet, V<sub>IN</sub> = 3.6V, T<sub>CASE</sub> = 100°C, TSOPJW-12:  $R_{DS(ON)L}$  = 75m $\Omega$ ,  $R_{DS(ON)H}$  = 220m $\Omega$ ,  $\theta_{JA}$  = 160°C/W.

$$\begin{aligned} \mathsf{P}_{\mathsf{LOSS}(\mathsf{RDSON})} &= \mathsf{I}_{\mathsf{RMS}^2} \cdot (\mathsf{R}_{\mathsf{DS}(\mathsf{ON})\mathsf{L}} + \mathsf{R}_{\mathsf{DS}(\mathsf{ON})\mathsf{H}}) \\ &= 0.527^2 \, (0.220 + 0.075) \\ &= (0.527)^2 \, (0.295) \\ &= 0.082 \\ &= 82 \text{mW} \end{aligned}$$

$$T_{J(MAX)} = T_{AMB} + \theta_{JA} \cdot P_{LOSS(RDSON)}$$

$$= 50 + 160 (0.082)$$

$$= 50 + 13.1$$

$$= 61.3^{\circ}C$$

| Manufacturer | Part Number | Rated I <sub>F(AV)</sub><br>Current (A) <sup>1</sup> | Rated<br>Voltage (V) | Thermal<br>Resistance<br>(θ <sub>JA</sub> , °C/W)¹ | Case    |

|--------------|-------------|------------------------------------------------------|----------------------|----------------------------------------------------|---------|

| Diodes, Inc. | B340LA      | 3.00                                                 | 40                   | 25                                                 | SMA     |

| Diodes, Inc. | SD103AWS    | 0.35                                                 | 30                   | 625                                                | SOD-323 |

| Diodes, Inc. | BAT42WS     | 0.20                                                 | 30                   | 625                                                | SOD-323 |

| Diodes, Inc. | B0520WS     | 0.50                                                 | 20                   | 426                                                | SOD-323 |

| ON Semi      | MBR130LSFT  | 1.00                                                 | 30                   | 325                                                | SOD-123 |

| ON Semi      | MBR0530T    | 0.50                                                 | 30                   | 206                                                | SOD-123 |

| Zetex        | ZHCS350     | 0.35                                                 | 40                   | 330                                                | SOD-523 |

| Zetex        | BAT54       | 0.20                                                 | 30                   | 330                                                | SOT-23  |

Table 3: Typical Surface Mount Schottky Rectifiers for Various Output Loads. (select  $T_J < 110^{\circ}C$  in application circuit).

| Manufacturer | Part Number    | Inductance<br>(µH) | Max DC I <sub>SAT</sub><br>Current (A) | DCR<br>(Ω) | Size (mm)<br>LxWxH | Туре         |

|--------------|----------------|--------------------|----------------------------------------|------------|--------------------|--------------|

| Sumida       | CDR4D11/HP-2R4 | 2.4                | 1.70                                   | 105        | 4.8x4.8x1.2        | Shielded     |

| Sumida       | CDRH4D18-2R2   | 2.2                | 1.32                                   | 75         | 5.0x5.0x2.0        | Shielded     |

| Murata       | LQH55DN2R2M03  | 2.2                | 3.20                                   | 29         | 5.0x5.7x4.7        | Non-Shielded |

| Murata       | LQY33PN2R2M02  | 2.2                | 0.72                                   | 360        | 3.2x3.2x0.85       | Non-Shielded |

| Taiyo Yuden  | NR40182R2      | 2.2                | 2.70                                   | 60         | 4.0x4.0x1.8        | Shielded     |

| Taiyo Yuden  | NR30152R2      | 2.2                | 1.48                                   | 60         | 3.0x3.0x1.5        | Shielded     |

| Taiyo Yuden  | NR40102R2      | 2.2                | 1.15                                   | 150        | 4.0x4.0x1.0        | Shielded     |

| Taiyo Yuden  | CBC3225T2R2MR  | 2.2                | 1.13                                   | 80         | 3.2x2.5x2.5        | Non-Shielded |

| Coiltronics  | SD3814-2R2     | 2.2                | 1.90                                   | 77         | 3.8x3.8x1.4        | Shielded     |

| Coiltronics  | SD3114-2R2     | 2.2                | 1.48                                   | 86         | 3.1x3.1x1.4        | Shielded     |

| Coiltronics  | SD3112-2R2     | 2.2                | 1.12                                   | 140        | 3.1x3.1x1.2        | Shielded     |

Table 4: Typical Surface Mount Inductors for Various Output Loads (select  $I_{PEAK} < I_{SAT}$ ).

| Manufacturer | Part Number        | Туре    | Value<br>(μF) | Voltage<br>(V) | Temp. Co. | Footprint<br>LxWxH (mm) |

|--------------|--------------------|---------|---------------|----------------|-----------|-------------------------|

| Murata       | GRM188R60J475KE19D | Ceramic | 2.2           | 6.3            | X5R       | 0603                    |

| Murata       | GRM188R61A225KE34D | Ceramic | 2.2           | 10             | X5R       | 0603                    |

| Murata       | GRM188R61C225KA88  | Ceramic | 2.2           | 16             | X5R       | 0805                    |

| Murata       | GRM21BR61E225KA12L | Ceramic | 2.2           | 25             | X5R       | 0805                    |

| Murata       | GRM188R61E105KA12D | Ceramic | 1.0           | 25             | X5R       | 0603                    |

**Table 5: Typical Surface Mount Capacitors for Various Output Loads.**

<sup>1.</sup> Results may vary depending on test method used and specific manufacturer.

## **Ordering Information**

| Package   | Marking <sup>1</sup> | Part Number (Tape and Reel) <sup>2</sup> |

|-----------|----------------------|------------------------------------------|

| TSOPJW-12 | RDXYY                | AAT1230ITP-T1                            |

| TDFN34-16 |                      |                                          |

All AnalogicTech products are offered in Pb-free packaging. The term "Pb-free" means semiconductor products that are in compliance with current RoHS standards, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. For more information, please visit our website at http://www.analogictech.com/pbfree.

## **Package Information**

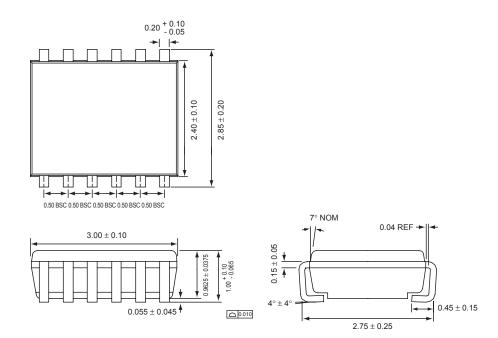

#### TSOPJW-12

All dimensions in millimeters.

<sup>1.</sup> XYY = assembly and date code.

<sup>2.</sup> Sample stock is generally held on part numbers listed in BOLD.

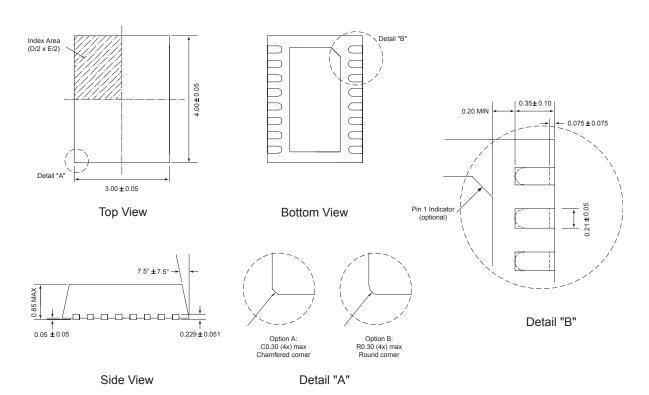

#### **TDFN34-16**

All dimensions in millimeters.

© Advanced Analogic Technologies, Inc.

AnalogicTech cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in an AnalogicTech product. No circuit patent licenses, copyrights, mask work rights, or other intellectual property rights are implied. AnalogicTech reserves the right to make changes to their products or specifications or to discontinue any product or service without notice. Customers are advised to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability. AnalogicTech warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with AnalogicTech's standard warranty. Testing and other quality control techniques are utilized to the extent AnalogicTech deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed.

# Advanced Analogic Technologies, Inc.

830 E. Arques Avenue, Sunnyvale, CA 94085 Phone (408) 737-4600 Fax (408) 737-4611